# DP83858 100 Mb/s TX/T4 Repeater Interface Controller (100RIC8<sup>™</sup>)

### **General Description**

The DP83858 100 Mb/s TX/T4 Repeater Interface Controller, known as 100RIC8, is designed specifically to meet the needs of today's high speed Ethernet networking systems. The DP83858 is fully compatible with the IEEE 802.3 repeater's clause 27. This device is targeted at low port count managed and unmanaged repeater applications.

The DP83858 supports up to eight 100 Mb/s links with its network interface ports. The 100RIC8 can be configured to be used with either 100BASE-TX or 100BASE-T4 PHY technologies. Larger repeaters may be constructed by cascading DP83858s together using the built-in Inter Repeater bus.

In conjunction with a DP83856 100 Mb/s Repeater Information Base device, a DP83858 based repeater becomes a managed entity that is compatible with IEEE 802.3u (clause 30), collecting and providing an easy interface to all the required network statistics.

### **Features**

■ IEEE 802.3u repeater and management compatible

- Supports Class II TX translational repeater and Class I T4 repeater

- Supports 8 network connections (ports)

- Up to 31 repeater chips cascadable for larger hub applications--may use DP83858 in conjunction with DP83850 100RIC (12 ports per chip)

- Separate jabber and partition state machines for each port

- Management interface to DP83856 allows all repeater MIBs to be maintained

- Large per-port management counters reduces management CPU overhead

- On-chip elasticity buffer for PHY signal re-timing to the DP83858 clock source

- Serial register interface reduces cost

- Physical layer device control/status access available via the serial register interface

- Detects repeater identification errors

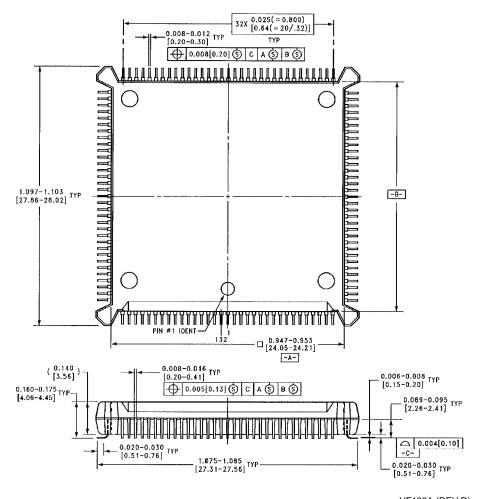

- 132 pin PQFP package

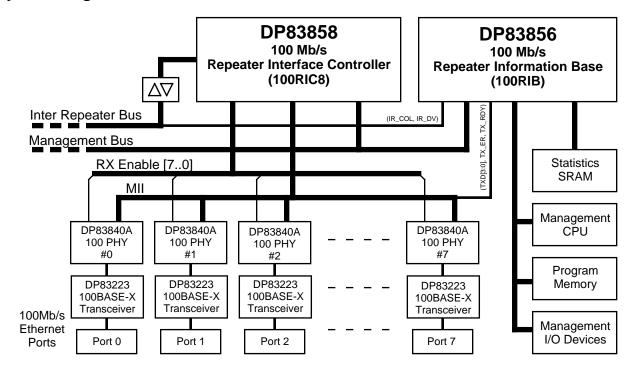

### **System Diagram**

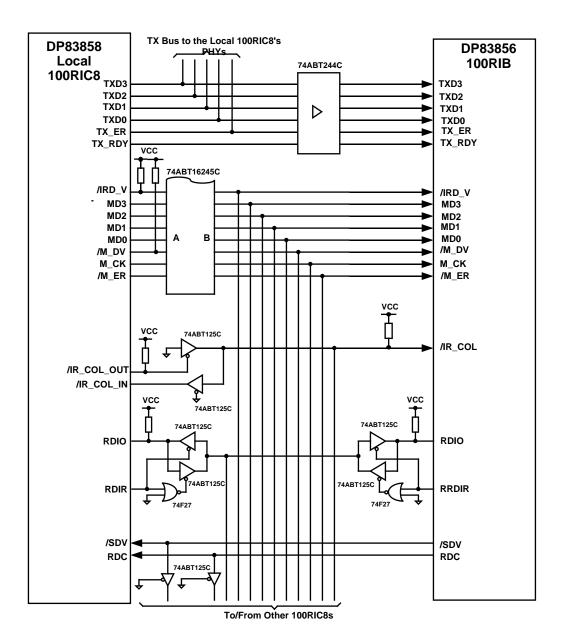

Note: The above system diagram depicts the repeater configured in 100BASE-TX mode.

FAST<sup>®</sup> is a registered trademark of Fairchild Semiconductor Corporation. TRI-STATE<sup>®</sup> is a registered trademark of National Semiconductor Corporation. 100RIC<sup>™</sup> is a trademark of National Semiconductor Corporation.

|     |        | Table of                                    | Con | tents      |                                                                        |

|-----|--------|---------------------------------------------|-----|------------|------------------------------------------------------------------------|

| 1.0 | Pin Co | onnection Diagram                           | 4.0 | Regist     | ters                                                                   |

|     | 1.1    | Pin Table                                   |     | 4.1        | Page 0 Register Map                                                    |

| 2.0 | Pin De | escription                                  |     | 4.2        | Page 1 Register Map                                                    |

|     | 2.1    | Physical Layer Interface                    |     | 4.3        | Configuration Register (CONFIG)                                        |

|     | 2.2    | Inter Repeater and Management Bus Interface |     | 4.4<br>4.5 | Page Register (PAGE)                                                   |

|     | 2.3    | EEPROM Interface                            |     | 4.5<br>4.6 | Partition Status Register (PARTITION)  Jabber Status Register (JABBER) |

|     | 2.4    | Miscellaneous                               |     | 4.7        | Administration Register (ADMIN)                                        |

|     | 2.5    | Pin Type Designation                        |     | 4.8        | Device ID Register (DEVICEID)                                          |

| 3.0 | Functi | onal Description                            |     | 4.9        | Hub ID 0 Register (HUBID0)                                             |

|     | 3.1    | Repeater State Machine                      |     | 4.10       | Hub ID 1 Register (HUBID1)                                             |

|     | 3.2    | RXE Control                                 |     | 4.11       | Port Management Counter Registers                                      |

|     | 3.3    | TXE Control                                 |     | 4.12       | Silicon Revision Register (SIREV)                                      |

|     | 3.4    | Data Path                                   | 5.0 | DP838      | 358 Applications                                                       |

|     | 3.5    | Elasticity Buffer                           |     | 5.1        | MII Interface Connections                                              |

|     | 3.6    | Jabber Protection State Machine             |     | 5.2        | Repeater ID Interface                                                  |

|     | 3.7    | Auto-Partition State Machine                |     | 5.3        | Inter Repeater Bus Connections                                         |

|     | 3.8    | Inter Repeater Bus Interface                |     | 5.4        | DP83856 100RIB Connections                                             |

|     | 3.9    | Management Bus                              |     | 5.5        | Port Partition and Jabber Status LEDs                                  |

|     | 3.10   | Management Event Flags and Counters         | 6.0 | AC an      | d DC Specifications                                                    |

|     | 3.11   | Serial Register Interface                   |     | 6.1        | DC Specifications                                                      |

|     | 3.12   | Jabber/Partition LED Driver Logic           |     | 6.2        | AC Specifications                                                      |

|     | 3.13   | EEPROM Serial Read Access                   | 7.0 | Physic     | cal Dimensions                                                         |

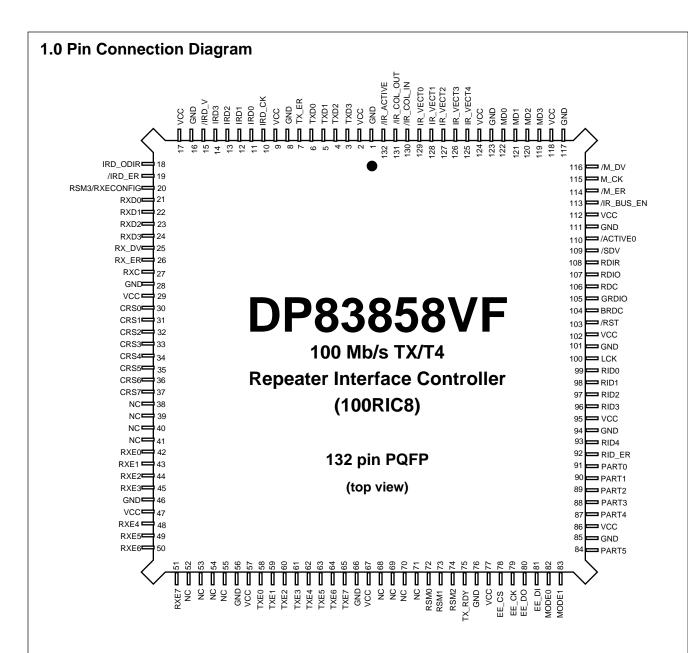

NC: These pins shall not have any connections and are reserved by National for future use.

Pinout subject to change. Please contact National Semiconductor for the latest design information.

Order Number DP83858VF NS Package Number VF132A

| Pin Name          | Pin No.                                                           | Section    |

|-------------------|-------------------------------------------------------------------|------------|

| /ACTIVEO          | 110                                                               | 2.2        |

| /IR_ACTIVE        | 132                                                               | 2.2        |

| /IR_BUS_EN        | 113                                                               | 2.2        |

| /IR_COL_IN        | 130                                                               | 2.2        |

| /IR_COL_OUT       | 131                                                               | 2.2        |

| /IRD_ER           | 19                                                                | 2.2        |

| /IRD_V            | 15                                                                | 2.2        |

| /M_DV             | 116                                                               | 2.2        |

| /M_ER             | 114                                                               | 2.2        |

| /RST              | 103                                                               | 2.4        |

| /SDV              | 109                                                               | 2.2        |

| BRDC              | 104                                                               | 2.4        |

| CRS[7:0]          | 37-30                                                             | 2.1        |

| EE_CK             | 79                                                                | 2.3        |

| EE_CS             | 78                                                                | 2.3        |

| EE_DI             | 81                                                                | 2.3        |

| EE_DO             | 80                                                                | 2.3        |

| GND               | 1, 8, 16, 28, 46, 56, 66,76, 85, 94, 101, 111, 117,123            | N/A        |

| GRDIO             | 105                                                               | 2.4        |

| IR_VECT[4:0]      | 125-129                                                           | 2.2        |

| IRD[3:0]          | 14-11                                                             | 2.2        |

| IRD_CK            | 10                                                                | 2.2        |

| IRD_ODIR          | 18                                                                | 2.4        |

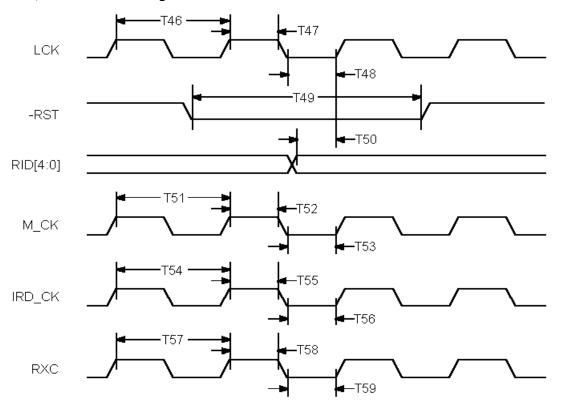

| LCK               | 100                                                               | 2.4        |

| M_CK              | 115                                                               | 2.2        |

| MD[3:0]           | 119-122                                                           | 2.2        |

| MODE[1:0]         | 83-82                                                             | 2.4        |

| PART[5:0]         | 84, 87-91                                                         | 2.4        |

| RDC               | 106                                                               | 2.2        |

| RDIO              | 107                                                               | 2.2        |

| RDIR              | 108                                                               | 2.4        |

| RID[4:0]          | 93, 96-99                                                         | 2.4        |

| RID_ER            | 92                                                                | 2.4        |

| RSM[2:0]          | 74-72                                                             | 2.4        |

|                   |                                                                   | 2.4        |

| RSM[3]/ RXECONFIG | 20                                                                |            |

| RX_DV             | 25                                                                | 2.1        |

| RX_ER             | 26                                                                | 2.1        |

| RXC               | 27                                                                | 2.1        |

| RXD[3:0]          | 24-21                                                             | 2.1        |

| RXE[7:0]          | 51-48, 45-42                                                      | 2.1        |

| TX_ER             | 7                                                                 | 2.1        |

| TX_RDY            | 75                                                                | 2.1        |

| TXD[3:0]          | 3-6                                                               | 2.1        |

|                   |                                                                   | 2.1<br>N/A |

| TXE[7:0] VCC      | 65-58<br>2, 9, 17, 29, 47, 57, 67, 77, 86, 95, 102, 112, 118, 124 |            |

# 2.0 Pin Descriptions

# 2.1 Physical Layer Interface

| Signal Name | Type | Active     |                                                                                                                             |                                  | Description                                                                                                                                                                                            |

|-------------|------|------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD[3:0]    | I    | _          | ported.                                                                                                                     |                                  | a inputs from each Physical layer chip. Up to 12 ports are sup-                                                                                                                                        |

|             |      |            | Note: Input b                                                                                                               |                                  |                                                                                                                                                                                                        |

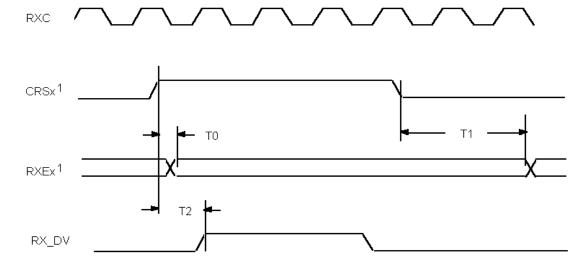

| RXE[7:0]    | O, L | high (low) |                                                                                                                             | pins are eith                    | d to the respective Physical Layer chip to enable its Receive er active high or active low depending on the polarity of RSM3                                                                           |

|             |      |            | RXE[7:0]                                                                                                                    | RSM3                             |                                                                                                                                                                                                        |

|             |      |            | Active High                                                                                                                 | Unconnect                        | ed or pulled high                                                                                                                                                                                      |

|             |      |            | Active Low                                                                                                                  | Pulled dow                       | n                                                                                                                                                                                                      |

| RX_DV       | I    | high       | Receive Data                                                                                                                | a Valid: Ass                     | erted High when valid data is present on RXD[3:0].                                                                                                                                                     |

|             |      |            | preted as "log                                                                                                              | gic one" by th<br>tion on this p | ng idle, when 100PHYs TRI-STATE®, this signal is NOT interne repeater, a $1k\Omega$ pull down resistor must be placed on this bull down should be between the repeater and the nearest trine repeater. |

| RX_ER       | I    | high       | When this sig                                                                                                               | nal is assert<br>as shown be     | cal Layer asserts this signal high when it detects receive error. ted, the 100PHY (TX or T4) device indicates the type of error blow. Note that this data is passed only to the Inter Repeater Bus:    |

|             |      |            | RX_ER                                                                                                                       | RXD[3:0]                         | Receive Error Condition                                                                                                                                                                                |

|             |      |            | 0                                                                                                                           | data                             | Normal data reception                                                                                                                                                                                  |

|             |      |            | 1                                                                                                                           | 0h                               | Symbol code violation                                                                                                                                                                                  |

|             |      |            | 1                                                                                                                           | 1h <sup>1</sup>                  | Elasticity Buffer Over/Under-run                                                                                                                                                                       |

|             |      |            | 1                                                                                                                           | 2h                               | Invalid Frame Termination                                                                                                                                                                              |

|             |      |            | 1                                                                                                                           | 3h <sup>2</sup>                  | Reserved                                                                                                                                                                                               |

|             |      |            | 1                                                                                                                           | 4h <sup>2</sup>                  | 10Mb Link Detected                                                                                                                                                                                     |

|             |      |            | <sup>1</sup> The 100PH code will nev                                                                                        | Y must be co                     | onfigured with the Elasticity Buffer bypassed; hence this error ated.                                                                                                                                  |

|             |      |            | <sup>2</sup> These error<br>the DP83858<br>never be pas                                                                     | only enable                      | nly appear when CRS from the 100PHY is not asserted. Since s a 100PHY when its CRS is asserted, these error codes will the chip.                                                                       |

|             |      |            | Note: Input b                                                                                                               | uffer has a v                    | veak pull-down.                                                                                                                                                                                        |

| RXC         | I    | _          |                                                                                                                             |                                  | ed clock from the Physical Layer device. RXD, RX_DV, and m the falling edge of this clock.                                                                                                             |

|             |      |            | Note: Input b                                                                                                               | uffer has a v                    | veak pull-down.                                                                                                                                                                                        |

| CRS[7:0]    | I    | high       | Carrier Sens                                                                                                                | e: Asynchro                      | nous carrier indication from the Physical Layer device.                                                                                                                                                |

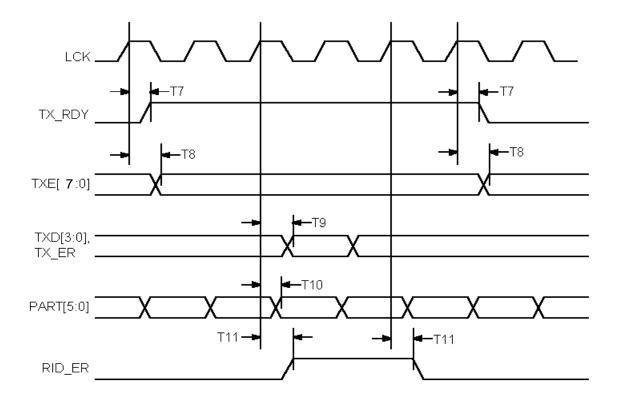

| TXE[7:0]    | O, L | high       |                                                                                                                             |                                  | es corresponding port for transmitting data.                                                                                                                                                           |

| TX_RDY      | O, L | high       | <b>Transmit Ready</b> : Indicates when a transmit is in progress. Essentially, this signal is the logical 'OR' of all TXEs. |                                  |                                                                                                                                                                                                        |

| TX_ER       | O, M | high       | Transmit Err                                                                                                                | or: Asserted                     | d high when a code violation is requested to be transmitted.                                                                                                                                           |

| TXD[3:0]    | O, H | high       | Transmit Da                                                                                                                 | <b>ta</b> : Nibble da            | ata output to be transmitted by each Physical Layer device.                                                                                                                                            |

Note: A table showing pin type designation is given in section 2.5

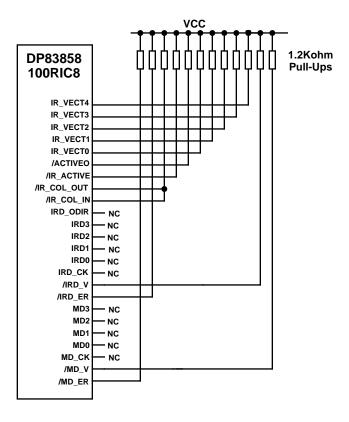

# 2.2 Inter Repeater and Management Bus Interface

| Signal Name  | Type      | Active   | Description                                                                                                                                                                                                                                                                                                             |

|--------------|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

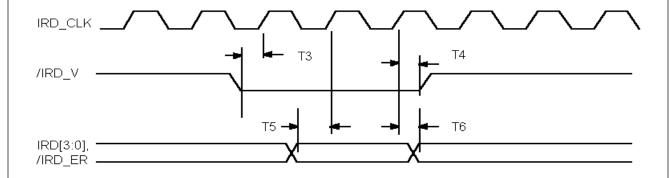

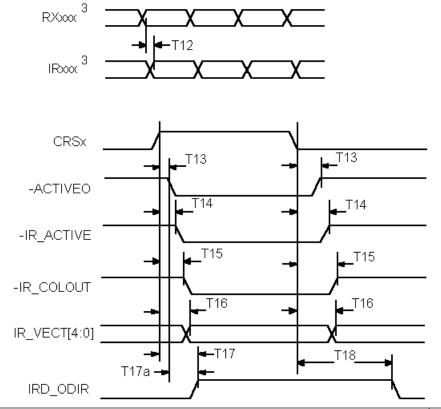

| IRD[3:0]     | I/O/Z, M  | _        | Inter Repeater Data: Nibble data input/output. Transfers data from the "active" DP83858 to all other "inactive" DP83858s. The bus master of the IRD bus is determined by IR_VECT bus arbitration.                                                                                                                       |

|              |           |          | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                                                  |

| /IRD_ER      | I/O/Z, M  | low      | Inter Repeater Data Error: This signal carries the RX_ER state across the Inter Repeater bus. Used to track receive errors from the physical layer in real-time                                                                                                                                                         |

| /IRD_V       | I/O/Z, M  | low      | Inter Repeater Data Valid: This signal carries the inverted RX_DV state across the Inter Repeater bus. It is used to frame good packets.                                                                                                                                                                                |

|              |           |          | Note: A recommended 1.5K pull-up prevents first repeated packet corruption .                                                                                                                                                                                                                                            |

| IRD_CK       | I/O/Z, M  | _        | <b>Inter Repeater Data Clock:</b> All Inter Repeater signals are synchronized to the rising edge of this clock.                                                                                                                                                                                                         |

|              |           |          | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                                                  |

| IRD_ODIR     | O, L      | high     | Inter Repeater Data Outward Direction: This pin indicates the direction of data fo an external transceiver. It is HIGH when IRD[3:0], /IRD_V, /IRD_CK, and /IRD_ER are driven out towards the Inter Repeater bus, and LOW when data is being received from the bus.                                                     |

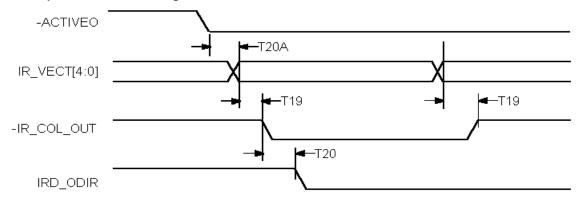

| /IR_ACTIVE   | I/O/OC, M | low      | <b>Inter Repeater Activity</b> : This "open-collector" type output is asserted when the repeater senses network activity.                                                                                                                                                                                               |

|              |           |          | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                                                  |

| /IR_COL_IN   | I         | low      | Inter Repeater Collision In: Indication from another DP83858 that it senses two or more ports receiving or another DP83858 has detected a collision.                                                                                                                                                                    |

|              |           |          | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                                                  |

| /IR_COL_OUT  | O/OC, M   | low      | Inter Repeater Collision Out: Asserted when the DP83858 senses two or more ports receiving or non-idle, either 1) within this DP83858 or 2) in another DP83858 using the IR_VECT number to decide (the IR_VECT number read will differ from the number of this DP83858 if another device is active).                    |

| IR_VECT[4:0] | I/O/OC, M | high     | Inter Repeater Vector: When the repeater senses at least one of its ports active, i drives its unique vector (from RID[4:0]) onto these pins. If the vector value read back differs from its own (because another vector is being asserted by another device), then this DP83858 will:                                  |

|              |           |          | 1) not drive IRD_ODIR signal and,                                                                                                                                                                                                                                                                                       |

|              |           |          | 2) tri-states the IRD[3:0], /IRD_ER, /IRD_V, and IRD_CK signals.                                                                                                                                                                                                                                                        |

|              |           |          | However, if the value read back is the same as its own RID number, this DP83858 will continue to drive the Inter Repeater bus signals. Note that these vectors are driver onto the bus for the duration of /ACTIVEO assertion.                                                                                          |

|              |           |          | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                                                  |

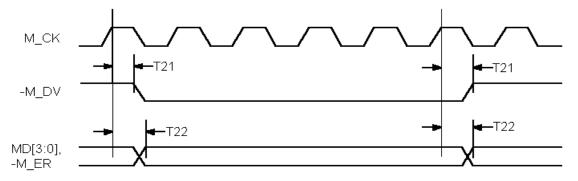

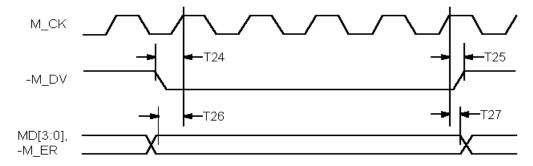

| MD[3:0]      | I/O/Z, M  | high     | <b>Management Data:</b> Outputs management information for the DP83856 management chip. During packet reception the DP83858 drives its RID number and the por number of the receiving port onto this bus.                                                                                                               |

|              |           |          | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                                                  |

| /M_DV        | I/O/Z, M  | low      | Management Data Valid: Asserted when valid data is present on MD[3:0].                                                                                                                                                                                                                                                  |

|              |           |          | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                                                  |

| M_CK         | I/O/Z, M  | _        | <b>Management Clock</b> : All data transfers on the management bus are synchronize to the rising edge of this clock.                                                                                                                                                                                                    |

|              |           | <u> </u> | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                                                  |

| /M_ER        | I/O/Z, M  | low      | Management Error: Asserted when an Elasticity Buffer overrun or under-run error has been detected.                                                                                                                                                                                                                      |

| //D DIIO 51: | 0.1       |          | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                                                  |

| /IR_BUS_EN   | O,L       | low      | Inter-Repeater Bus Enable: This signal is asserted at all times (either when the 100RIC8 is driving the bus or receiving from the bus) and it is deasserted only when the 100RIC8 switches direction from an input (receiving) mode to an output (driving) mode. After this switch, this signal becomes asserted again. |

| Signal Name | Type     | Active | Description                                                                                                                                                                                                                                                                              |

|-------------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

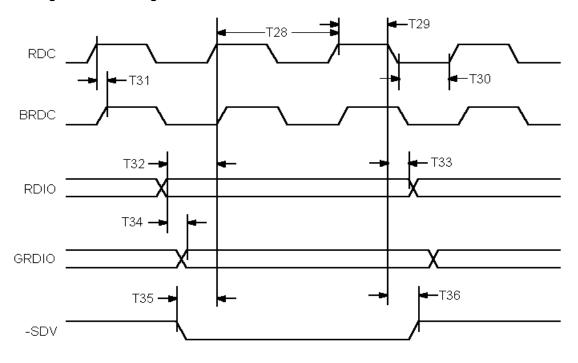

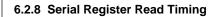

| RDIO        | I/O/Z, L | _      | <b>Register Data I/O</b> : Serial data input/output transfers data to/from the internal registers. Serial protocol conforms to the IEEE 802.3u MII (Media Independent Interface) specification.                                                                                          |

|             |          |        | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                   |

| RDC         | I        | _      | <b>Register Data Clock</b> : All data transfers on RDIO are synchronized to the rising edge of this clock. RDC is limited to a maximum frequency of 2.5 MHz. At least 3 cycles of RDC must be provided during assertion of /RST (pin 103) to ensure proper reset of all internal blocks. |

| /SDV        | I        | low    | <b>Serial Data Valid</b> : Asserted when a valid read or write command is present. Used to detect disconnection of the management bus so that synchronization is not lost. If not used, tie this pin to GND.                                                                             |

|             |          |        | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                   |

| /ACTIVEO    | O/OC, M  | low    | <b>Active Out</b> : Enable for the IR_VECT[4:0] and /IR_ACTIVE signals. Used in multi-DP83858 systems to enable the external buffers driving these Inter Repeater Bus signals.                                                                                                           |

|             |          |        | A pull up of 680 $\Omega$ must be used with this signal.                                                                                                                                                                                                                                 |

Note: A table showing pin type designation is given in section 2.5

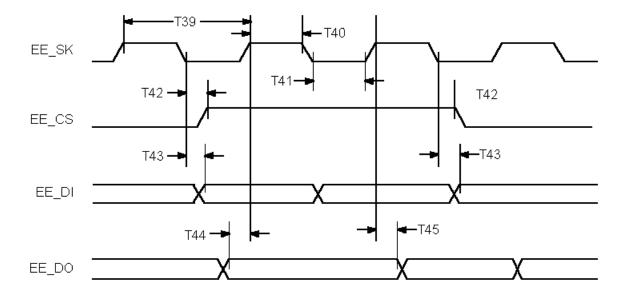

### 2.3 EEPROM Interface

| Signal Name | Туре | Active | Pin Description                                                                 |

|-------------|------|--------|---------------------------------------------------------------------------------|

| EE_CS       | O, L | high   | EEPROM Chip Select: Asserted during reads to EEPROM.                            |

| EE_CK       | O, L | _      | <b>EEPROM Serial Clock</b> : Local Clock ÷ 32 = 0.78125MHz                      |

| EE_DO       | I    | _      | <b>EEPROM Serial Data Out</b> : Connected to the serial data out of the EEPROM. |

| EE_DI       | O, L |        | <b>EEPROM Serial Data In</b> : Connected to the serial data in of the EEPROM.   |

# 2.4 Miscellaneous

| Signal Name          | Туре        | Active | Pin Description                                                                                                                                                                                                                                                                                                                                      |  |

|----------------------|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LCK                  | I           | _      | <b>Local Clock</b> : Must be 25 MHz $\pm$ 50ppm. Used for TX data transfer to Physical Layer devices, TX Bus data transfers and DP83858 internal state machines.                                                                                                                                                                                     |  |

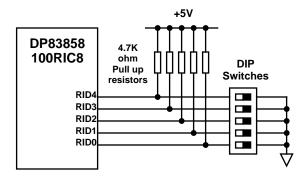

| RID[4:0]             | I           | _      | <b>Repeater Identification Number</b> : Provides the unique vector for the IR_VECT[4:0] signals used in Inter Repeater bus arbitration. These bit are also used to uniquely ider tify this chip for serial register accesses. The RID value is latched when reset is deasserted.                                                                     |  |

|                      |             |        | <b>Note</b> : The arbiter cannot use the value 1Fh as its arbitration vector. This is the IR_VECT[4:0] bus idle state, therefore RID[4:0] must never be set to this value.                                                                                                                                                                           |  |

| /RST                 | I           | low    | Reset: The chip is reset when this signal is asserted low.                                                                                                                                                                                                                                                                                           |  |

| GRDIO                | I/O/Z, L    | _      | <b>Gated Register Data Input/Output</b> : This I/O is a gated version of RDIO. When the "phy_access" bit in the CONFIG register is set high, the RDIO signal is passed through to GRDIO for accessing the physical layer chips.                                                                                                                      |  |

|                      |             |        | Note: Input buffer has a weak pull-up.                                                                                                                                                                                                                                                                                                               |  |

| BRDC                 | O, L        | _      | <b>Buffered Register Data Clock</b> : Buffered version of RDC. Allows more devices to be chained on the MII serial bus.                                                                                                                                                                                                                              |  |

| RDIR                 | O, L        | high   | <b>Register Data Direction</b> : Direction signal for an external bi-directional buffer on the RDIO signal.                                                                                                                                                                                                                                          |  |

|                      |             |        | 0 = RDIO data flows into the DP83858                                                                                                                                                                                                                                                                                                                 |  |

|                      |             |        | 1 = RDIO data flows out of the DP83858                                                                                                                                                                                                                                                                                                               |  |

|                      |             |        | Defaults to 0 when no register access is present.                                                                                                                                                                                                                                                                                                    |  |

| PART[5:0]            | O, L        | _      | <b>Partition</b> : Used to indicate each port's Jabber and Partition status. PART[3:0] cycle through each port number (0-11) continuously. PART[4] indicates the Partition status for each port (1 = Port Partitioned). PART[5] indicates the Jabber status for each port (1 = Port Jabbering). These pins are intended to be decoded to drive LEDs. |  |

| RID_ER               | O, L        | high   | <b>Repeater ID Error</b> : This pin is asserted under the conditions which set the RID_error bit in the DEVICEID register.                                                                                                                                                                                                                           |  |

| RSM[3]<br>/RXECONFIG | I/O, L      | _      | Repeater State Machine Output/ RXE Polarity: This pin is an input during reset and it is used to latch the desired polarity of RXE[7:0] signals.                                                                                                                                                                                                     |  |

|                      |             |        | When this pin is pulled high or it is unconnected, then the RXE signals become active high. However, if this signal is pulled low, then the RXE signals become active low.                                                                                                                                                                           |  |

|                      |             |        | In all other non-reset times, this pin reflects the output of the Repeater State Machine.                                                                                                                                                                                                                                                            |  |

| RSM[3]               | I/O, L O, L | _      | Test Outputs indicating the state of the Repeater State Machine.                                                                                                                                                                                                                                                                                     |  |

| RSM[2:0]             |             |        | RSM[3:0] State                                                                                                                                                                                                                                                                                                                                       |  |

|                      |             |        | 0 idle                                                                                                                                                                                                                                                                                                                                               |  |

|                      |             |        | 1 collision                                                                                                                                                                                                                                                                                                                                          |  |

|                      |             |        | 2 one port left                                                                                                                                                                                                                                                                                                                                      |  |

|                      |             |        | 3 repeat                                                                                                                                                                                                                                                                                                                                             |  |

|                      |             |        | 4 noise                                                                                                                                                                                                                                                                                                                                              |  |

|                      |             |        | Other states are undefined.                                                                                                                                                                                                                                                                                                                          |  |

| MODE[1:0]            | I           | _      | Mode Inputs: The 100RIC8 may be configured in the following modes:                                                                                                                                                                                                                                                                                   |  |

|                      |             |        | MODE[1:0] Operation                                                                                                                                                                                                                                                                                                                                  |  |

|                      |             |        | 0,0 No special modes selected                                                                                                                                                                                                                                                                                                                        |  |

|                      |             |        | 1,0 Test mode                                                                                                                                                                                                                                                                                                                                        |  |

|                      |             |        |                                                                                                                                                                                                                                                                                                                                                      |  |

|                      |             |        | 0,1 Test mode                                                                                                                                                                                                                                                                                                                                        |  |

**Note**: A table showing pin type designation is given in section 2.5

### 2.5 Pin Type Designation

| Pin Type | Description                                                                                    |

|----------|------------------------------------------------------------------------------------------------|

| ı        | Input Buffer                                                                                   |

| 0        | Output Buffer, driven high or low at all times                                                 |

| I/O/Z    | Bi-directional Buffer with high impedance output                                               |

| O/Z      | Output Buffer with high impedance capability                                                   |

| OC       | Open Collector like signals. These buffers are either driven low or in a high-impedance state. |

| L        | Output low drive: 4 mA                                                                         |

| М        | Output medium drive: 12 mA                                                                     |

| Н        | Output high drive: 24 mA                                                                       |

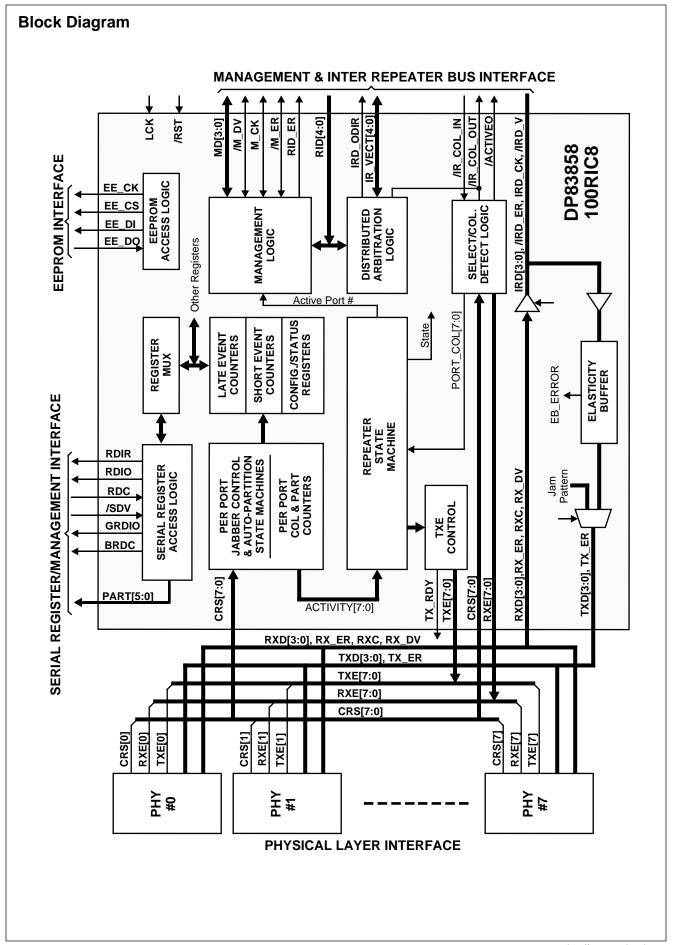

### 3.0 Functional Description

The following sections describe the different functional blocks of the DP83858 100 Mb/s Repeater Interface Controller. The IEEE 802.3u repeater specification details a number of functions a repeater system is required to perform. These functions are split between those tasks that are common to all data channels and those that are specific to each individual channel. The DP83858 follows this split task approach for implementing the required functions. Where necessary, the difference between the TX and T4 modes is discussed.

#### 3.1 Repeater State Machine

The Repeater State Machine (RSM) is the main block that governs the overall operation of the repeater. At any one time, the RSM is in one of the following states: Idle, Repeat, Collision, One Port Left, or Noise.

#### 3.1.1 Idle State

The RSM enters this state after reset or when there is no activity on the network and the carrier sense is not present. The RSM exits from this state if the above conditions are no longer true.

### 3.1.2 Repeat State

This state is entered when there is a reception on only one of the ports, port N. While in this state, the data is transmitted to all the ports except the receiving port (port N). The RSM either returns to Idle state when the reception ends, or transitions to Collision state if there is reception activity on more than one port.

### 3.1.3 Collision State

When there is receive activity on more than one port of the repeater, the RSM moves to Collision state. In this state, transmit data is replaced by Jam and sent out to all ports including the original port N.

There are two ways for the repeater to leave the Collision state. The first is when there is no receive activity on any of the ports. In this case, the repeater moves to Idle state. The second is when there is only one port experiencing collision in which case the repeater enters the One Port Left state.

### 3.1.4 One Port Left State

This state is entered only from the Collision state. It guarantees that repeaters connected hierarchically will not jam each other indefinitely. While in this state, Jam is sent out to all ports except the port that has the receive activity. If

more receive activity occurs on any other port, then the repeater moves to Collision state.

Otherwise, the repeater will transition to Idle state when the receive activity ends.

#### 3.1.5 Noise State

When there is an Elasticity Buffer overflow or underflow during packet reception, then the repeater enters the Noise state. During this state, the Jam pattern is sent to all transmitting ports. The repeater leaves this state by moving either to the Idle state, if there is no receive activity on any ports, or to the Collision state, if there is a collision on one of its segments.

#### 3.2 RXE Control

When only one port has receive activity, the RXE signal (receive enable) is activated. If multiple ports are active (i.e. a collision scenario), then RXE will not be enabled for any port. The Port Select Logic asserts the open-collector outputs /IR\_COL\_OUT and /IR\_ACTIVE to indicate to other cascaded DP83858s that there is collision or receive activity present on this DP83858.

The polarity of the RXE signal can be set through an external pull down resistor placed at the RSM[3] pin. That is, if the RSM[3] pin is unconnected or pulled high, then the RXE is active high and when the RSM[3] is pulled low, then the RXE is active low.

#### 3.3 TXE Control

This control logic enables the appropriate ports for data transmission according to the four states of the RSM. For example, during Idle state, no ports are enabled; during Repeat state, all ports but port N are enabled; in Collision state, all ports including port N are enabled; during One Port Left state, all ports except the port experiencing the collision will be enabled.

#### 3.4 Data Path

After the Port Selection logic has enabled the active port, receive data (RXD), receive clock (RXC), receive error (RX\_ER) and receive data valid (RX\_DV) will flow through the chip from that port out onto the Inter Repeater (IR) bus if no collisions are present. The signals on the IR bus flow either in to or out of the chip depending upon the Repeater's state.

If the DP83858 is currently receiving and no collisions are present, the IR signals flow out of the chip. The DP83858's Arbitration Logic guarantees that only one DP83858 will gain ownership of the IR bus. In all other states, the IR signals are inputs.

When IR signals are inputs, the signals flow into the Elasticity Buffer (EB). Here, the data is re-timed and then sent out to the transmit ports. The Transmit Control logic determines which ports are enabled for data transmission.

If a collision occurs, a Jam pattern is sent out from the EB instead of the data. The Jam pattern (3,4,3,4,.... from the DP83858, encoded by the Physical Layer device as 1,0,1,0,....) is transmitted for the duration of the collision activity.

If the repeater is configured in the preamble regeneration mode (T4 mode), approximately 12 clock cycles after the assertion of /IR\_ACTIVE (indicating a packet reception on a segment), the 100RIC8 begins to transmit the preamble pattern onto the other network segments. While the pre-

amble is being transmitted, the EB monitors the received clock and data signals. When the start of the frame delimiter "SFD" is detected, the received data stream is written into the EB. After this point, data from the EB is sent out to the Transmit interface. The preamble is always generated in its entirety (i.e. fifteen 5's and one D) even if a collision occurs

### 3.5 Elasticity Buffer

The elasticity buffer, or a logical FIFO buffer, is used to compensate for the variations and timing differences between the recovered Receive Clock and the local clock. This buffer supports maximum clock skews of 200 ppm for the preamble regeneration (T4) mode, and 100 ppm for the TX mode, within a maximum packet size of 1518 bytes.

#### 3.6 Jabber Protection State Machine

The jabber specification for 100BASE-T is functionally different than 10BASE-T.

In 10BASE-T, each port's Jabber Protect State machine ensures that Jabber transmissions are stopped after 5ms and followed by 96 to 116 bit times silence before the port is re-enabled.

In 100BASE-T, when a port jabbers, its receive and transmit ports are cutoff until the jabber activity ceases. All other ports remain unaffected and continue normal operation. The 100BASE-T Jabber Protect Limit (that is, the time for which a port can jabber until it is cutoff) for the DP83858 is reached if the CRS is active for more than 655µs.

A jabbering port that is cut off will be re-enabled when the jabber activity ceases and the IDLE line condition is sensed.

#### 3.7 Auto-Partition State Machine

In order to protect the network from a port that is experiencing excessive consecutive collisions, each port must have its own auto-partition state machine.

A port with excessive consecutive collisions will be partitioned after a programmed number of consecutive collisions occur on that port. Transmitting ports will not be affected.

The DP83858 has a configuration bit that allows the user to choose how many consecutive collisions a port should experience before partitioning. This bit can be set for either 32 or 64 consecutive collisions. The IEEE802.3u 100BASE-T standard specifies the consecutive collisions limit as greater than 60. A partitioned port will be reconnected when a collision-free packet of length 512 bits or more (that is, at least a minimum sized packet) is transmitted out of that port.

The DP83858 also provides a configuration bit that disables the auto-partition function completely.

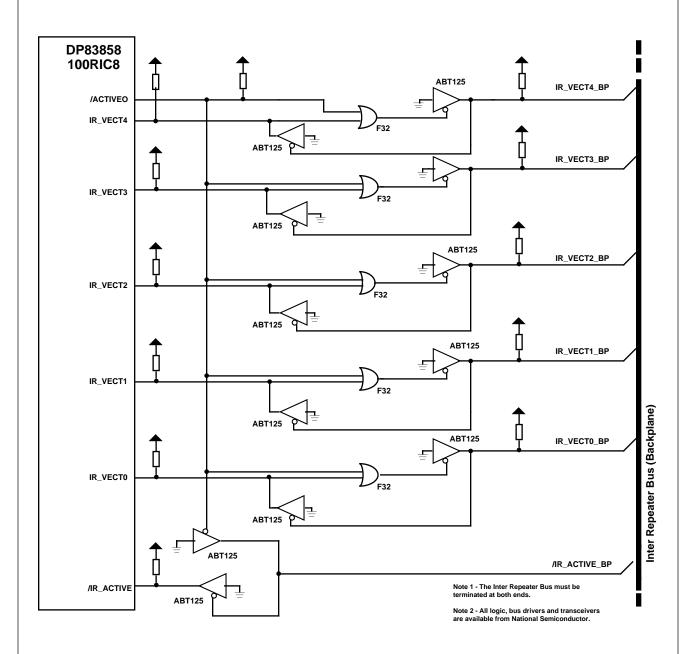

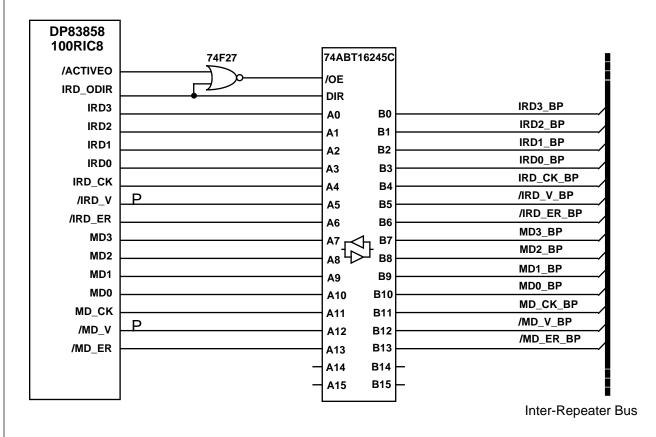

#### 3.8 Inter Repeater Bus Interface

The Inter Repeater bus is used to connect multiple DP83858s together to form a logical repeater unit and also to allow a managed entity. The IR bus allows received data packets to be transferred from the receiving DP83858 to the other DP83858s in the system. These DP83858s then send the data stream to their transmit enabled ports.

Notification of collisions to other cascaded DP83858s is as important as data transfer across the network. The arbitration logic asynchronously determines if more than one 100RIC8, cascaded together, are receiving simultaneously. The IR bus has a set of status lines capable of conveying

collision information between DP83858s to ensure their main state machines operate in the appropriate manner.

The IR bus consists of the following signals:

- Inter Repeater Data. This is the transfer data, in nibble format, from the active DP83858 to all other cascaded DP83858s.

- Inter Repeater Data Error. This signal carries the receive error status from the physical layer in real-time.

- Inter Repeater Data Valid. This signal is used to frame good packets.

- Inter Repeater Data Clock. All IR data is synchronized to this clock.

- Inter Repeater Data Outward Direction. This pin indicates the direction of the data flow with respect to the DP83858. When the DP83858 is driving the IR bus (i.e. it contains port N) this signal is HIGH and when the DP83858 is receiving data from other DP83858s over the IR bus this signal is LOW.

- Inter Repeater Bus Enable. This signal (connected to the /ENABLE pin of the external transceivers on the IR bus) is used in conjunction with the IRD ODIR signal (connected to the DIR pin of the transceivers) to TRI-STATE these transceivers during the change of direction from input to output, or vice versa. This signal is always active allowing the IR bus signals to pass through the transceivers into or out of the 100RIC8. However when the 100RIC8 switches from input mode (IRD\_ODIR=0) to output mode (IRD\_ODIR=1), the /IR\_BUS\_EN signal is deasserted allowing the transceivers to TRI-STATE during the direction change. After this turn-around, this signal is asserted back again. (IRD\_ODIR assertion (high) to /IR\_BUS\_EN low timing is a minimum of 0.1 ns. and a maximum of 1.0. The time from /IR\_BUS\_EN (high) to the IRD\_ODIR high is a minimum of 10 ns. and a maximum of 20 ns. In addition, /ACTIVEO assertion (low) to /IR\_BUS\_EN high timing is a maximum of 1.0

- Inter Repeater Activity. When there is network activity the DP83858 asserts this output signal.

- Inter Repeater Collision Output. If there are multiple receptions on ports of a DP83858 or if the DP83858 senses concurrent activity on another DP83858 it asserts this output.

- Inter Repeater Collision Input. This input indicates that one of the cascaded DP83858s is experiencing a collision.

- Inter Repeater Vector. When there is reception on a port the DP83858 drives a unique vector onto these lines. The vector on the IR bus is compared with the Repeater ID (RID). The DP83858 will continue to drive the IR bus if both the vector and RID match.

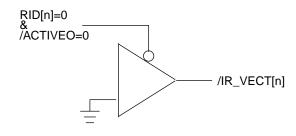

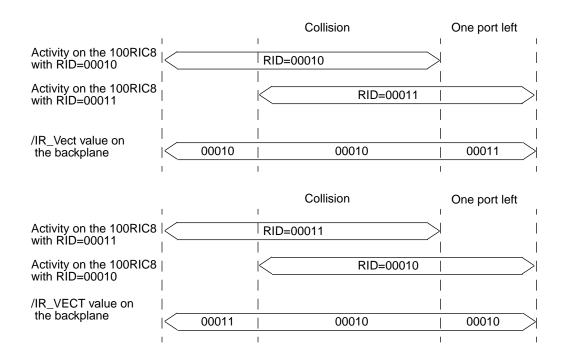

The following figure shows the conditions that cause an open collector vector signal to be asserted on the backplane bus.

Figure 1. Open Collector /IR\_VECT[n]

As seen, if the RID[n]=1, and the repeater is receiving on a port, then the /IR\_VECT[n] value would be 1 due to the pull-up on this pin. In the case that RID[n]=0, then a zero is driven out on the /IR\_VECT[n] signal.

As an example assume that two repeaters with RIDs equal to RID #1=00010 and RID #2=00011 are connected through the Inter-RIC bus. The following diagrams depict the values of /IR\_VECT signals over the backplane.

Active Output. This signal is asserted by a DP83858 when at least one of its ports is active. It is used to enable external bus transceivers.

Figure 2. RID to /IR\_VECT Mapping

### 3.9 Management Bus

The task of network statistics gathering in a repeater system is divided between the DP83858 and DP83856 devices. Together, these devices collect all the required management information (compliant to IEEE 802.3u clause 30) associated with a packet.

Each time a packet is received by a DP83858, it drives the device and the port number onto the management bus in 3 contiguous nibbles of data.

During a single reception, only one DP83858 drives this information onto the management bus. During a collision, the management bus will TRI-STATE (because the information on this bus becomes invalid).

The first nibble of management data contains the least significant 4 bits of the RID number, the second contains the most significant bit of the RID number and the third contains the number of the receiving port.

When the 100RIC8 is not receiving a packet, it monitors the RID numbers from other 100RIC8s. If there is a match between any of these numbers and 100RIC8's own RID, then a RID contention error signal (RID\_ER) is asserted.

The management bus also indicates whether an elasticity buffer error (due to under-run or over-run) has occurred by asserting the /M\_ER signal.

### 3.10 Management Event Flags and Counters

Repeater management statistics are supported either directly by using the DP83858's on-chip event flags and counters, or indirectly, by the DP83858 providing the information to the DP83856 via the management and transmit bus.

Management information is maintained within the DP83858 in two ways: event flags and counters.

### 3.10.1 Event Flags

These are the events that provide a snapshot of the operation of the DP83858. These events include:

- Auto-Partition State, indicating whether a port is currently partitioned.

- Jabber State, indicating whether a port is in jabber state.

- Administration State, indicating if a port is disabled.

#### 3.10.2 Event Counters

The event counters maintain the statistics for events that occur too frequently for polled flags, or are collision oriented. Each port has its own set of event counters that keep track of the following events:

- Port Collisions. A 32-bit counter providing the number of collision occurrences on a port.

- Port Partitions. A 16-bit counter indicating the number of times that the port has partitioned.

- Late Events. A 32-bit counter indicating the number of times that a collision took place after 512 bit times (nominal). In the case of late events, both the late event and the collision counters will be incremented.

■ Short Events. A 32-bits wide counter indicating the number of packets whose length is 76 bits (nominal) or less.

### 3.11 Serial Register Interface

The DP83858 has 64 registers held in two pages of 32 (Register Page 0 and Register Page 1). The registers are 16 bits wide. Only one page of registers can be accessed at a time.

After power-up and/or reset, the DP83858 defaults to Register Page 0. Register Page 1 can be accessed by writing 0001h to the PAGE register in Register Page 0, whereupon further accesses will be to Register Page 1. Subsequently writing 0000h to the PAGE register in Register Page 1 switches the registers back to Register Page 0.

All accesses to DP83858 registers and counters, and to the connected Physical Layer devices (via the DP83858), are performed serially using the RDIO and RDC pins. The RDC clock is limited to a frequency no greater than 2.5MHz. This interface implements the serial management protocol defined by the MII specification, IEEE 802.3u clause 22. The protocol uses bit streams with the following format:

For Read operation: <start><opcode><device addr><reg addr> [turnaround] 0<data>.

For Write operation: <start><opcode><device addr><reg addr> <10><data>.

This protocol allows for up to 32 devices (DP83858s or other MII compliant devices) to be connected, each with a unique address and up to 32 16-bit registers. Devices are cascaded on the RDIO and RDC signals.

Since the RDIO pin is shared for both read and write operations, it must only be driven at the proper time. The serial protocol assumes that there is only one master (generally, the management entity's processor) and one or more slave devices (generally, the Physical Layer or DP83858 chips). The master drives RDIO at all times except when, during a slave read operation, the addressed slave places the serialized read data onto the RDIO line after the line turnaround field's first bit.

Unmanaged systems that do not use the DP83856 100RIB device for repeater management, it is important to provide the 100RIC with a minimum of 3 cycles of RDC during device reset. If the minimum number of cycles of RDC is not provided, the Serial Register Access Logic block may not be properly reset and as a result RDIO may not function properly. The 100RIB provides continuous RDC cycles, and eliminates this concern.

The fields of the protocol are defined in Table 3-1. In order for the protocol to work, all serial logic must first be "synchronized" to incoming data. A preamble of 32 consecutive 1's transmitted before the <start> field ensures "data lock".

This preamble only needs to be sent once (at reset). From then on, the <start> field lets the receive logic know where the beginning of the data frame occurs.

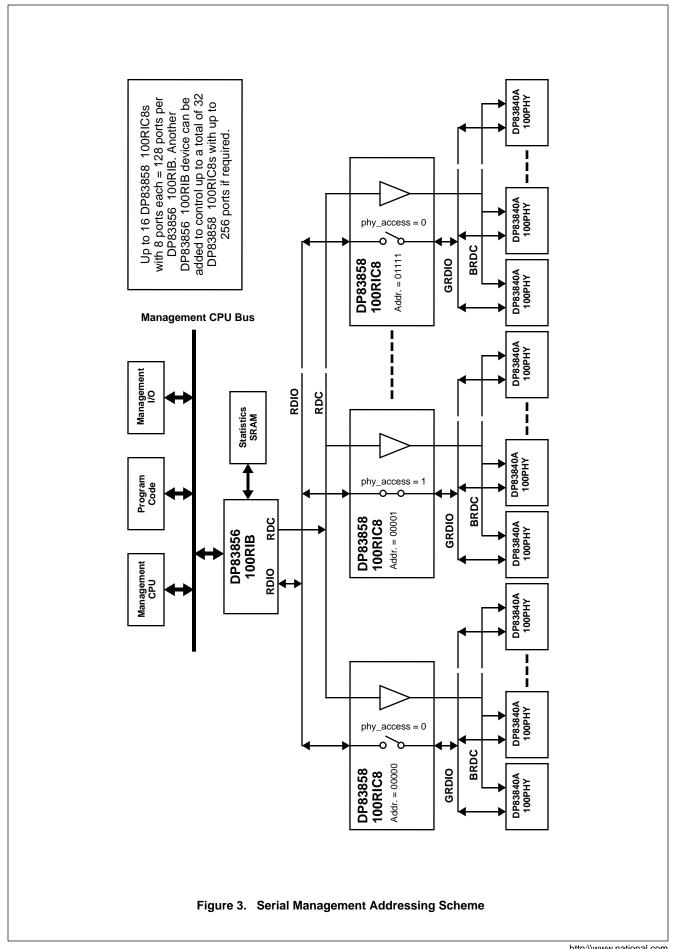

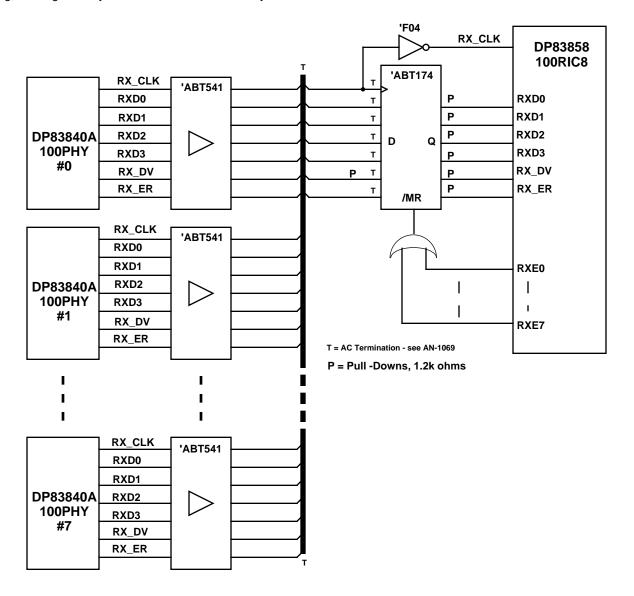

To access the Physical Layer devices via the serial bus, the DP83858 has a "phy\_access" mode. When in this mode, the register data input/output (RDIO) is gated to the GRDIO pin. This signal is connected to the serial data pins of the Physical Layer devices.

In this mode the buffers which drive RDIO and GRDIO will turn on in the appropriate direction for each serial access. In order to avoid possible contention problems, the user must ensure that only one DP83858 at a time has the "phy\_access" bit set. The CONFIG register contains the "phy\_access" bit, which can be set or cleared at any time.

Figure 3 shows a possible system implementation of the RDIO/GRDIO connection scheme. In this example, the DP83858 with address 00001 has its "phy\_access" bit set, allowing its eight DP83840A PHY devices to be accessed by the DP83856 100RIB.

MII serial management contention problems can be avoided by keeping to the addressing convention shown in Figure 3.

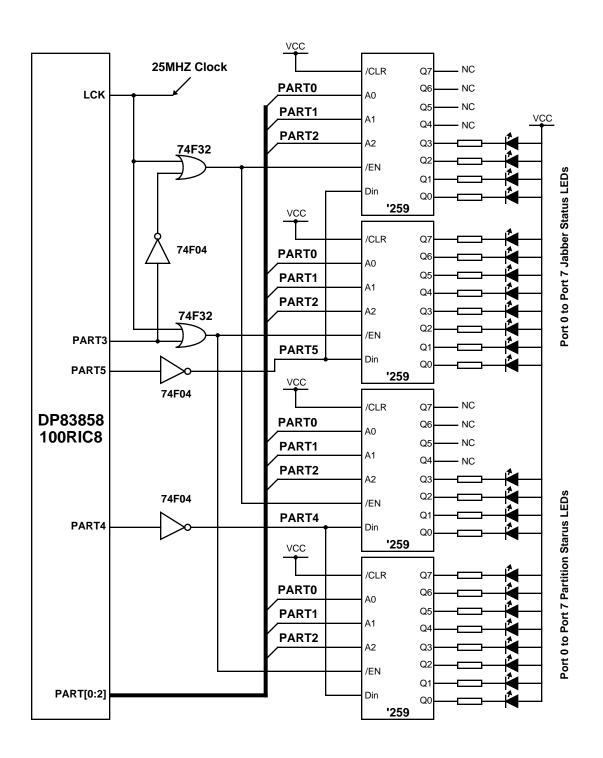

#### 3.12 Jabber/Partition LED Driver Logic

This logic encodes the current auto-partition status (from the PARTITION register) and the jabber status (from the JABBER register), and outputs this information to PART[5:0] pins. PART[3:0] cycles through each port num-

ber and PART[5:4] indicates the port's status. PART[5] indicates the Jabber status for each port (0 = LED OFF, 1 = LED ON - Port Jabbering). PART[4] indicates the Partition status for each port (0 = LED OFF, 1 = LED ON - Port Auto-Partitioned).

The port number on PART[3:0] is cycled with a 25MHz. External logic is required to decode the PART[5:0] outputs and drive the Partition and Jabber LEDs. Multi-color LEDs could be driven with the appropriate logic if required.

One possible implementation of a DP83858 Port Partition and Jabber Status LED scheme is given in section 5.5.

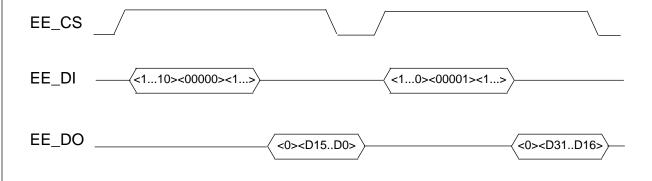

#### 3.13 EEPROM Serial Read Access

After reset is de-asserted, the DP83858 will serially read an NM93C06 EEPROM (or equivalent). Only the first 32-bits starting from address 0 will be read. Write access is not provided. The data is written to registers HUBID0 and HUBID1. The first bit read is written to HUBID0[0]; the last bit read will be written to HUBID1[15].

The DP83858 EEPROM interface implements the serial protocol as shown in Figure 3. The DP83858 will issue two read commands to obtain the 32-bit ID. The serial clock, EE\_CK will be continuous. For more explicit timing diagrams please refer to the NM93C06 datasheet.

The NM93C06 EEPROM must be pre-programmed with the HUBID value prior to fitting the device to the circuit since the DP83858 does not support programming of this device in circuit.

| Field                     | Encoding      | Description                                                  |

|---------------------------|---------------|--------------------------------------------------------------|

| <start></start>           | 01            | Indicates the beginning of an opcode operation.              |

| <opcode></opcode>         | 10            | Read                                                         |

|                           | 01            | Write                                                        |

|                           | all others    | Reserved                                                     |

| <reg addr=""></reg>       | 00000 - 11111 | Five bits are provided to address up to 32 16-bit registers. |

| <device addr=""></device> | 00000 - 11111 | Five bits are provided to address up to 32 devices.          |

Table 1. Serial Register Interface Encoding

Figure 4. Serial EEPROM Access Protocol

# 4.0 Registers

The DP83858 has 64 registers in 2 pages of 32 16-bit registers. At power-on and/or reset, the DP83858 defaults to Page 0 registers. The register page can be changed by writing to the PAGE register in either register page. The register page maps are given in sections 4.1 and 4.2, followed by a detailed description of the registers in sections 4.3 to 4.12.

### 4.1 Page 0 Register Map

| Address<br>(hex) | Name             | Access    | Description                                                                                                                                                                                                                                                                         |

|------------------|------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                | CONFIG           | r/w       | Sets the DP83858 configuration.                                                                                                                                                                                                                                                     |

| 1                | PAGE             | r/w       | Selects either register page 0 or 1.                                                                                                                                                                                                                                                |

| 2                | PARTITION        | read only | Indicates Auto-Partitioning status.                                                                                                                                                                                                                                                 |

| 3                | JABBER           | read only | Indicates Jabber status.                                                                                                                                                                                                                                                            |

| 4                | ADMIN            | r/w       | Port enable/disable, administration control/status.                                                                                                                                                                                                                                 |

| 5                | DEVICEID         | r/w       | Accesses a) the DP83858 ID number configured externally on the RID[4:0] pins and b) the last receiving port number. The DP83858 device number may be overwritten after it has been latched at the end of reset: be careful not to have duplicate ID's on the same IR bus interface. |

| 6                | HUBID0           | read only | First 16 bits read from EEPROM.                                                                                                                                                                                                                                                     |

| 7                | HUBID1           | read only | Second 16 bits read from EEPROM.                                                                                                                                                                                                                                                    |

| 8                | P0_SE            | r/w       | Port 0: 32-bit ShortEvent counter (See access rules section 4.11).                                                                                                                                                                                                                  |

| 9                | P0_LE            | r/w       | Port 0: 32-bit LateEvent counter (See access rules section 4.11).                                                                                                                                                                                                                   |

| Α                | P0_COL           | r/w       | Port 0: 32-bit Collision counter (See access rules section 4.11).                                                                                                                                                                                                                   |

| В                | P0_PART          | r/w       | Port 0: 16-bit Auto-Partition counter.                                                                                                                                                                                                                                              |

| С                | P1_SE            | r/w       | Port 1: 32-bit ShortEvent counter (See access rules section 4.11).                                                                                                                                                                                                                  |

| D                | P1_LE            | r/w       | Port 1: 32-bit LateEvent counter (See access rules section 4.11).                                                                                                                                                                                                                   |

| Е                | P1_COL           | r/w       | Port 1: 32-bit Collision counter (See access rules section 4.11).                                                                                                                                                                                                                   |

| F                | P1_PART          | r/w       | Port 1: 16-bit Auto-Partition counter.                                                                                                                                                                                                                                              |

| 10 - 13          | P2_SE<br>P2_PART | r/w       | Port 2 management counters (as per ports 0, 1 above).                                                                                                                                                                                                                               |

| 14 - 17          | P3_SE<br>P3_PART | r/w       | Port 3 management counters (as per ports 0, 1 above).                                                                                                                                                                                                                               |

| 18 - 1B          | P4_SE<br>P4_PART | r/w       | Port 4 management counters (as per ports 0, 1 above).                                                                                                                                                                                                                               |